## ELECTRONIC DEVICES AND ANALOG ELECTRONICS

Specially Designed for GATE Examination

Subscribe "Digcademy" youtube channel for topicwise videos of EDC & AE and join www.digcademy.com for getting free access to study material of EC,EE & IN

# ELECTRONIC DEVICES AND ANALOG ELECTRONICS

#### **VOLUME I**

First Edition 2021

# ELECTRONIC DEVICES AND ANALOG ELECTRONICS

#### **VOLUME I**

#### RAM NIWAS, IES

B.E. (NIT, Nagpur), M.E. (DCE, Delhi), Ph.D. (IIT, Delhi)

First Edition 2021

#### **DIGCADEMY**

E2/162, SECTOR 11, ROHINI, NEW -110085 Email : digcademy@gmail.com | www.digcademy.com

| First Edition 2021                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

| CODVELCUT © AUTHOD 2021                                                                                                                                                                                            |

| COPYRIGHT © AUTHOR, 2021 All rights reserved. No part of this publication may be reproduced, translated or transmitted in any form (except for review or criticism), without the written permission of the author. |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                    |

| Published by                                                                                                                                                                                                       |

| DIGCADEMY                                                                                                                                                                                                          |

| (A Unit of Daksh Bharat Society)                                                                                                                                                                                   |

| E2/162, Sector - 11, Rohini, New Delhi-10085                                                                                                                                                                       |

| Email: digcademy@gmail.com                                                                                                                                                                                         |

### CONTENTS

| HOW  | TO REAL                               | O THIS BOOK                                            | xiii |  |  |

|------|---------------------------------------|--------------------------------------------------------|------|--|--|

| PREF | ACE                                   |                                                        | xv   |  |  |

| GATE | SYLLAB                                | US                                                     | xvii |  |  |

| CHAF | TERWISI                               | E ANALYSIS OF GATE QUESTIONS                           | xix  |  |  |

|      |                                       |                                                        |      |  |  |

| CHAF | TER 1 SI                              | EMICONDUCTORS                                          | 1-74 |  |  |

| 1.1  | Atomic                                | Structure of Materials                                 |      |  |  |

| 1.2  | Bonding                               | g in solids                                            | 2    |  |  |

| 1.3  | Crystal                               | Geometry and Structure                                 | 2    |  |  |

| 1.4  | Energy                                | Band Theory of Crystals                                | 3    |  |  |

| 1.5  | Insulato                              | ors, Semiconductors and metals                         | 4    |  |  |

| 1.6  | Elemental and Compound Semiconductors |                                                        |      |  |  |

| 1.7  | Charge Carriers in Semiconductors     |                                                        |      |  |  |

| 1.8  | Intrinsio                             | e Semiconductors                                       | 7    |  |  |

|      | 1.8.1                                 | Band gap of Si and Ge                                  | 7    |  |  |

|      | 1.8.2                                 | Carrier Concentration in Intrinsic Semiconductors      | 8    |  |  |

|      | 1.8.3                                 | Important Properties of Ge, Si and GaAs Semiconductors | 8    |  |  |

| 1.9  | Extrinsi                              | c Semiconductors                                       | 8    |  |  |

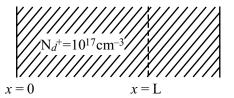

|      | 1.9.1                                 | n-type Semiconductors                                  | 9    |  |  |

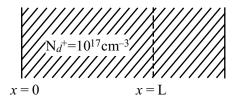

|      | 1.9.2                                 | p-type Semiconductors                                  | 9    |  |  |

|      | 1.9.3                                 | Charge Balance Equations of Extrinsic Semiconductors   | 10   |  |  |

| 1.10 | Law of I                              | Mass Action                                            | 11   |  |  |

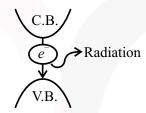

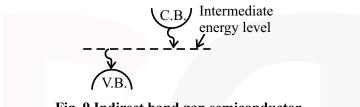

| 1.11 | Direct a                              | nd Indirect Band Gap Semiconductors                    | 13   |  |  |

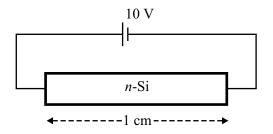

| 1.12 | Electric                              | al Properties of Semiconductors                        | 14   |  |  |

|      | 1.12.1                                | Conductivity                                           | 14   |  |  |

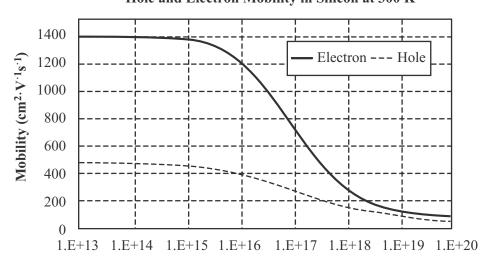

|      | 1.12.2                                | Mobility                                               | 15   |  |  |

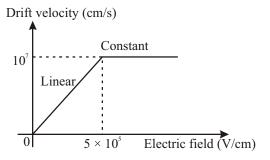

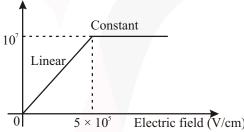

|      | 1.12.3                                | Drift velocity                                         | 15   |  |  |

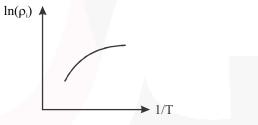

|       | 1.12.4                                          | Effect of temperature on conductivity of Semi-conductors                                   | 16 |  |

|-------|-------------------------------------------------|--------------------------------------------------------------------------------------------|----|--|

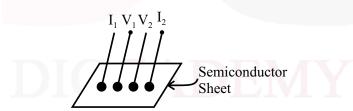

|       | 1.12.5                                          | Four Point Probe Method                                                                    | 20 |  |

|       | 1.12.6                                          | Conductivity Modulation                                                                    | 21 |  |

| 1.13  | Generation and Recombination of Charge Carriers |                                                                                            |    |  |

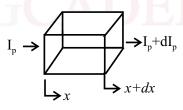

| 1.14  | Continu                                         | ity Equation                                                                               | 26 |  |

| 1.15  | Diffusion                                       | n                                                                                          | 27 |  |

| 1.16  | Einstein                                        | Relation                                                                                   | 29 |  |

| 1.17  | Compon                                          | nents of Current in Semiconductors                                                         | 30 |  |

|       | 1.17.1                                          | Drift Current                                                                              | 30 |  |

|       | 1.17.2                                          | Diffusion current                                                                          | 30 |  |

|       | 1.17.3                                          | Total Current                                                                              | 30 |  |

|       | 1.17.4                                          | Relationship between diffusion current of electrons and holes                              | 31 |  |

|       | 1.17.5                                          | Drift current of electrons and holes in terms of diffusion current of holes                | 31 |  |

|       | 1.17.6                                          | Diffusion Current of Injected Minority Carriers in                                         | 31 |  |

|       |                                                 | Semiconductors                                                                             |    |  |

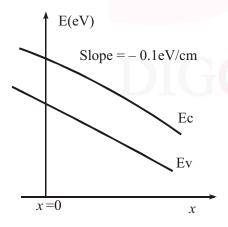

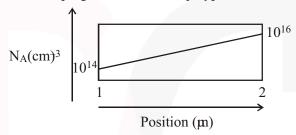

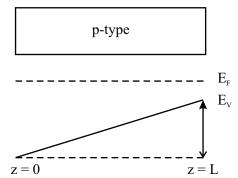

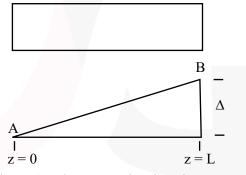

| 1.18  | Induce                                          | d Electric Field and Potential Variation in Graded                                         | 34 |  |

|       | 1 10 1                                          | Semiconductors                                                                             | 25 |  |

|       | 1.18.1                                          | Induced Electric Field and Variation of potential in step graded pn semiconductor junction | 35 |  |

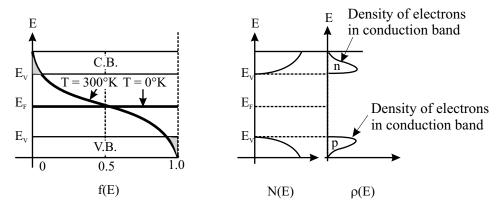

| 1.19. | Fermi L                                         | evel in Semiconductors                                                                     | 36 |  |

|       | 1.19.1                                          | Fermi-Dirac Function                                                                       | 36 |  |

|       | 1.19.2                                          | Density of States and Fermi-level in metals                                                | 37 |  |

|       | 1.19.3                                          | Concentration of Electrons and Holes in Semiconductors                                     | 37 |  |

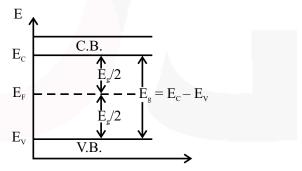

|       | 1.19.4                                          | Fermi Level in Intrinsic Semiconductor                                                     | 39 |  |

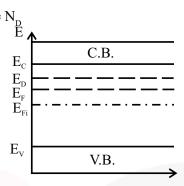

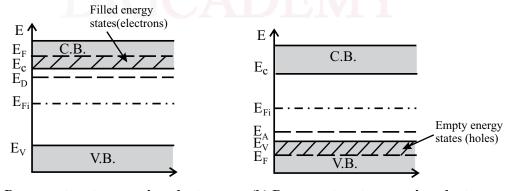

|       | 1.19.5                                          | Fermi Level in n-type Semiconductor                                                        | 40 |  |

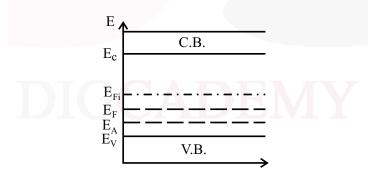

|       | 1.19.6                                          | Fermi Level in p-type Semiconductor                                                        | 42 |  |

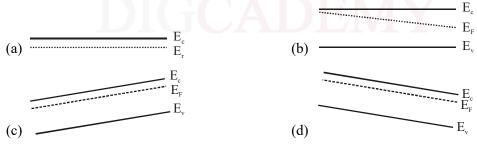

|       | 1.19.7                                          | Non-degenerate Semiconductors and Degenerate                                               | 44 |  |

|       |                                                 | Semiconductors                                                                             |    |  |

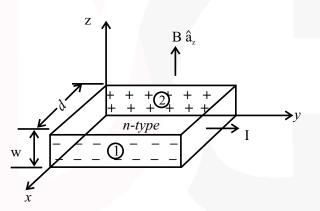

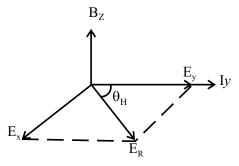

| 1 20  | Hall'e Fr                                       | ffect                                                                                      | 45 |  |

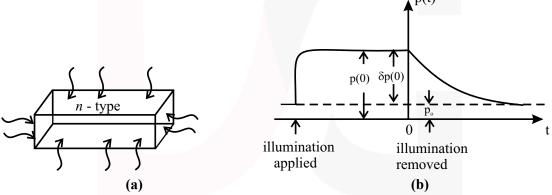

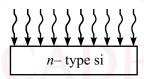

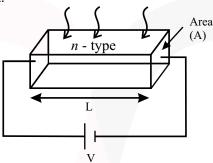

| 1.21 | Photoco        | nductor                                                     | 48     |  |  |

|------|----------------|-------------------------------------------------------------|--------|--|--|

| GATI | E QUEST        | IONS                                                        | 52     |  |  |

| Answ | vers & Ex      | planations OF GATE Questions                                | 60     |  |  |

|      |                |                                                             |        |  |  |

| CHAI | PTER 2 D       | OIODES                                                      | 75-184 |  |  |

| 2.1. | PN Junction 75 |                                                             |        |  |  |

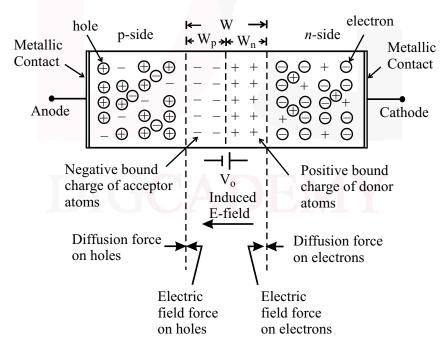

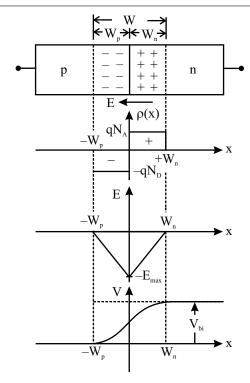

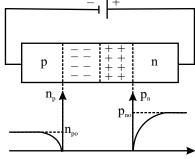

| 2.2  | Open Cir       | rcuited pn Junction                                         | 76     |  |  |

|      | 2.2.1          | Built-in Potential Barrier of Open Circuited pn Junction    | 76     |  |  |

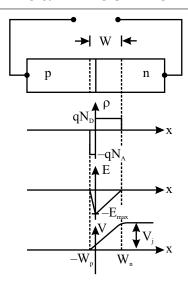

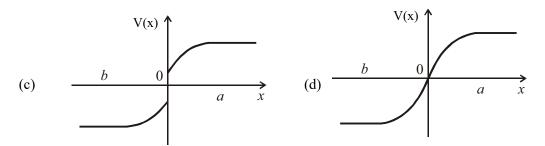

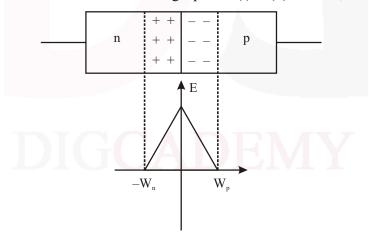

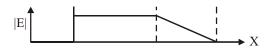

|      | 2.2.2          | Electric Field Intensity of Open Circuited pn Junction      | 78     |  |  |

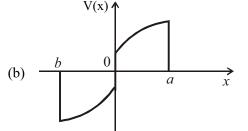

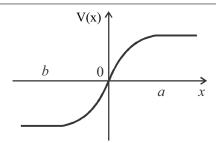

|      | 2.2.3          | Potential Function of Open Circuited pn Junction            | 80     |  |  |

|      | 2.2.4          | Space Charge or Depletion Layer Width of Open Circuited pn  | 81     |  |  |

|      |                | Junction                                                    |        |  |  |

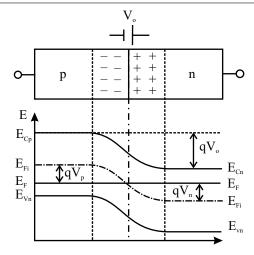

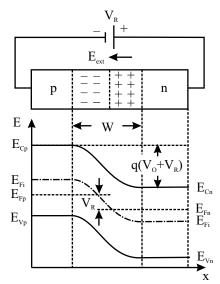

| 2.3  | Reverse        | Biased pn Junction                                          | 88     |  |  |

|      | 2.3.1          | Energy Band Diagram and Space Charge Width in Reverse       | 88     |  |  |

|      |                | Biased pn Junction                                          |        |  |  |

|      | 2.3.2          | Electric Field in Reverse Biased pn Junction                | 89     |  |  |

| 2.4  | Forward        | Biased pn Junction                                          | 90     |  |  |

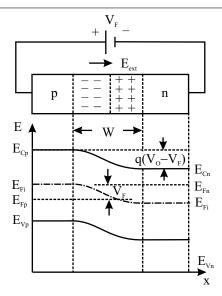

|      | 2.4.1          | Energy Band Diagram and Space Charge Width in Forward       | 90     |  |  |

|      |                | Biased pn Junction                                          |        |  |  |

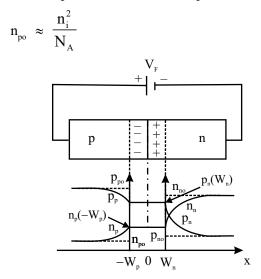

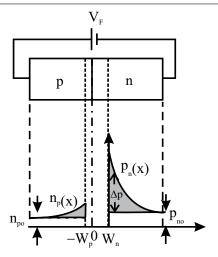

|      | 2.4.2          | Carrier Concentrations in Forward Biased pn Junction        | 91     |  |  |

| 2.5. | Generali       | zed Expression of Depletion Layer Width of pn Junctions and | 93     |  |  |

|      |                | Unipolar Junctions                                          |        |  |  |

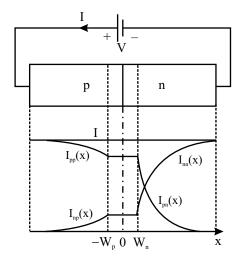

| 2.6. | Compon         | ents of Current in PN Junction Diode                        | 97     |  |  |

|      | 2.6.1          | Components of Currents in Forward Biased Diode              | 97     |  |  |

|      | 2.6.2          | Components of Currents in Reverse Biased Diode              | 99     |  |  |

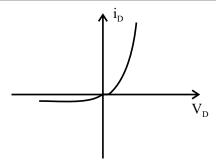

| 2.7  | Characte       | eristics of PN Junction Diode                               | 103    |  |  |

|      | 2.7.1          | V-I Characteristic                                          | 103    |  |  |

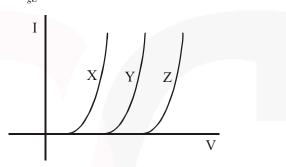

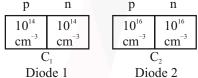

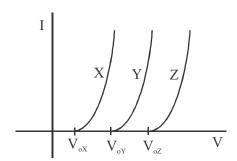

|      | 2.7.2          | Temperature Dependence of V-I characteristic of pn junction | 104    |  |  |

|      |                | diode                                                       |        |  |  |

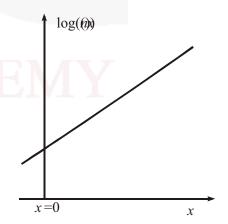

|      | 2.7.3          | Logarithmic Characteristic                                  | 104    |  |  |

|       | 2.7.4       | Piecewise Linear Characteristic                     | 105 |

|-------|-------------|-----------------------------------------------------|-----|

| 2.8   | Diode Re    | esistances                                          | 107 |

|       | 2.8.1       | Static Resistance of Diode                          | 107 |

|       | 2.8.2       | Dynamic Resistance of Diode                         | 107 |

| 2.9   | Diode Ca    | apacitances                                         | 109 |

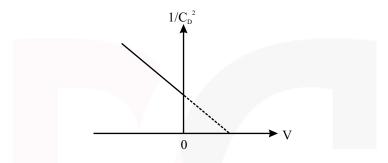

|       | 2.9.1       | Space Charge or Transition Capacitance              | 109 |

|       | 2.9.2       | Charge Control Description of Diode                 | 110 |

|       | 2.9.3       | Diffusion Capacitance or Storage Capacitance        | 112 |

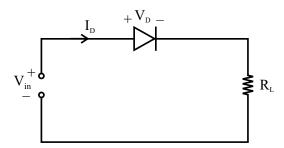

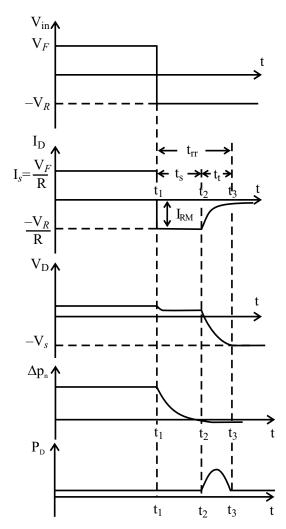

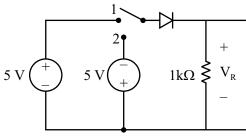

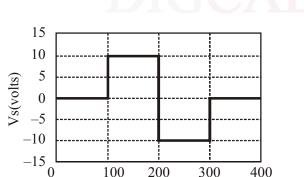

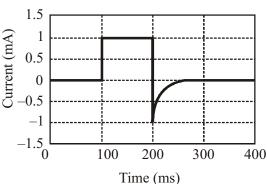

| 2.10. | Switchin    | ng Characteristics of pn Junction Diode             | 115 |

| 2.11  | DC Equi     | valent Circuit of an Diode                          | 118 |

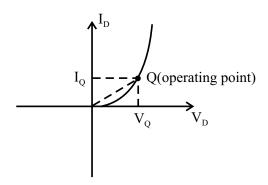

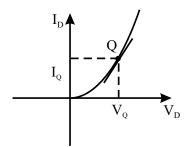

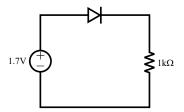

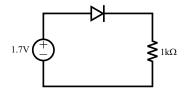

| 2.12. | Concept     | of Load Line of Diode                               | 120 |

| 2.13  | Small Si    | gnal Model of Diode                                 | 121 |

| 2.14  | Varactor    | diode                                               | 123 |

| 2.15  | Zener Diode |                                                     |     |

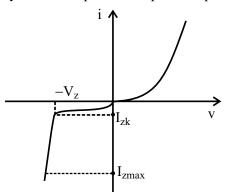

|       | 2.15.1      | V-I characteristic                                  | 124 |

|       | 2.15.2      | Mechanisms of breakdown                             | 124 |

|       | 2.15.3      | Breakdown Voltage of Zener Diode                    | 125 |

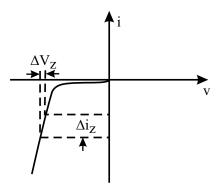

|       | 2.15.4      | Dynamic Resistance and Capacitance of Zener diode   | 126 |

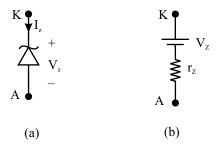

|       | 2.15.5      | Equivalent Circuit of Zener Diode                   | 127 |

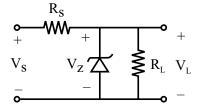

|       | 2.15.6      | Applications of Zener Diode                         | 127 |

| 2.16  | Tunnel o    | liode                                               | 128 |

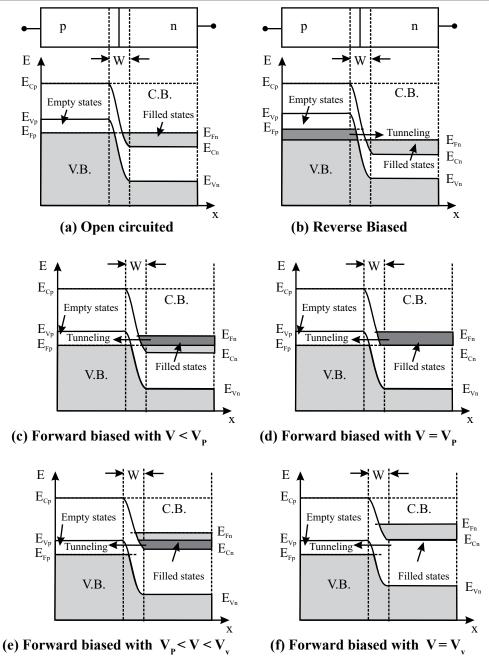

|       | 2.16.1      | Energy Band Diagram of Tunnel Diode                 | 128 |

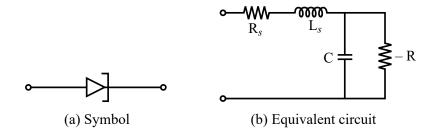

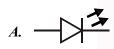

|       | 2.16.2      | Symbol and Equivalent circuit of Tunnel Diode       | 130 |

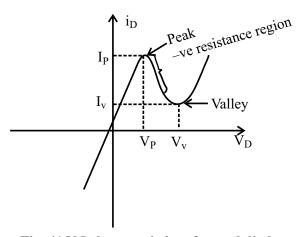

|       | 2.16.3      | V-I Characteristic of tunnel diode                  | 130 |

|       | 2.16.4      | Applications of Tunnel Diode                        | 131 |

|       | 2.16.5      | Advantages and Disadvantages                        | 131 |

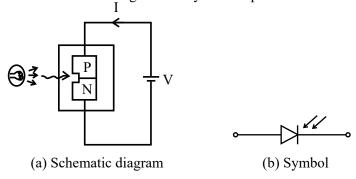

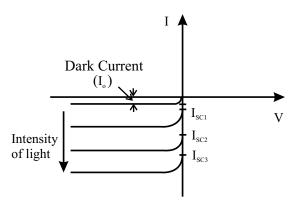

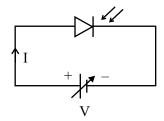

| 2.17  | PN June     | tion Photodiode                                     | 131 |

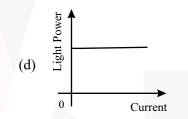

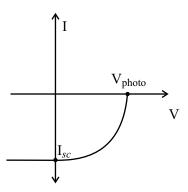

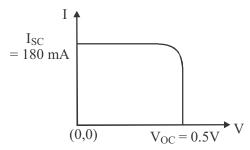

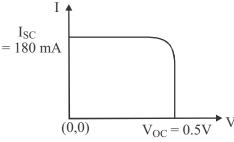

|       | 2.17.1      | VI Characteristics of Photodiode                    | 132 |

|       | 2.17.2      | Photo Current and Voltage of Illuminated Photodiode | 133 |

|       | 2 17 3      | Performance Parameters of Photodiode                | 133 |

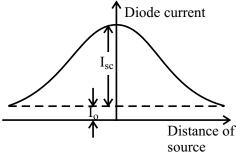

|      | 2.17.4                               | Relation in Solar Intensity and Photocurrent                    | 134        |  |  |

|------|--------------------------------------|-----------------------------------------------------------------|------------|--|--|

|      | 2.17.5                               | Applications of Photodiode                                      | 134        |  |  |

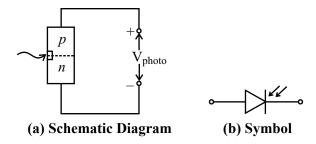

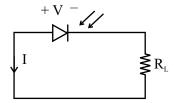

| 2.18 | Photovoltaic cell or Solar Cell      |                                                                 |            |  |  |

|      | 2.18.1                               | Working Principle of Solar Cell                                 | 135        |  |  |

|      | 2.18.2                               | Photovoltaic Potential or Photo voltage                         | 136        |  |  |

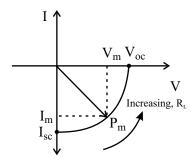

|      | 2.18.3                               | V-I Characteristics of Photovoltaic or Solar Cell               | 136        |  |  |

|      | 2.18.4                               | Output Power, Conversion Efficiency and Fill Factor of Solar of | cell 137   |  |  |

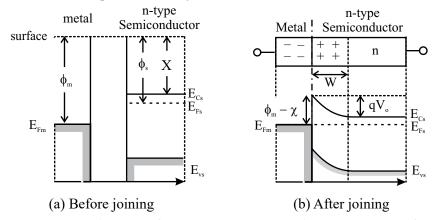

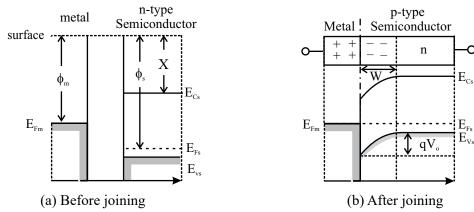

| 2.19 | Schottky                             | Diode                                                           | 141        |  |  |

|      | 2.19.1                               | Energy Band Diagram of Open Circuited Schottky Diode            | 142        |  |  |

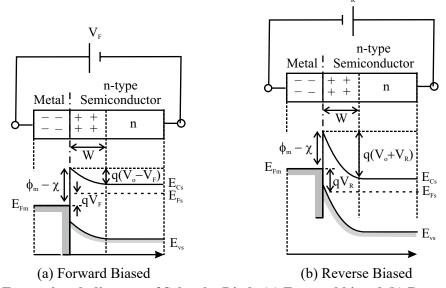

|      | 2.19.2                               | Energy Band Diagram of Forward Biased and Reverse Biased        | 143        |  |  |

|      |                                      | Schottky Diode                                                  |            |  |  |

|      | 2.19.3                               | Working of Schottky Barrier Diode                               | 144        |  |  |

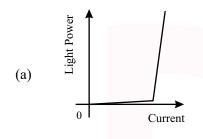

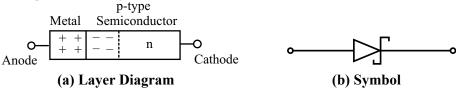

| 2.20 | Light Em                             | nitting Diode (LED)                                             | 145        |  |  |

| 2.21 | PIN diod                             | e                                                               | 146        |  |  |

| GATE | QUESTIC                              | ONS                                                             | 148        |  |  |

| Answ | ers & Exp                            | lanations of GATE Questions                                     | 160        |  |  |

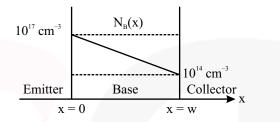

| СНАР | TER 3 BII                            | POLAR JUNCTION TRANSISTORS                                      | 185-236    |  |  |

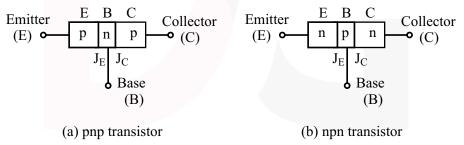

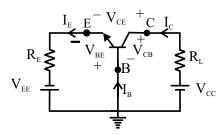

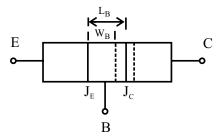

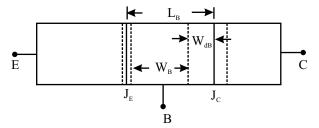

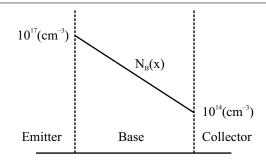

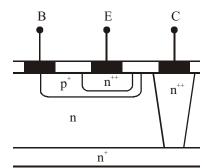

| 3.1  | Construc                             | ction of BJT                                                    | 185        |  |  |

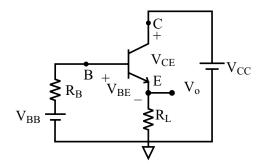

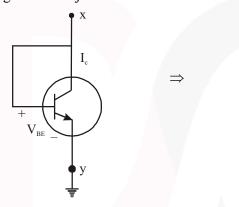

| 3.2  | Operatio                             | n of BJT as an Amplifier                                        | 186        |  |  |

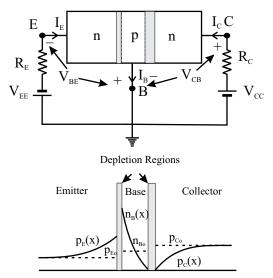

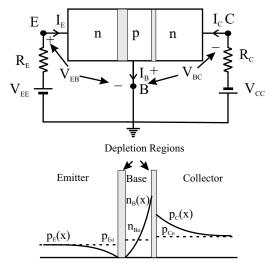

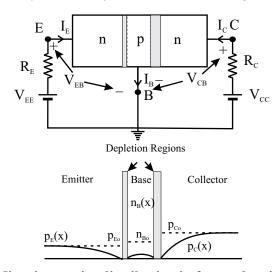

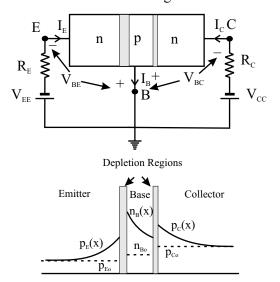

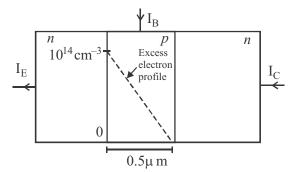

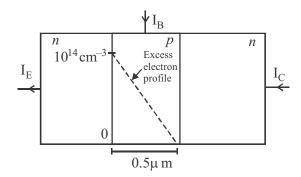

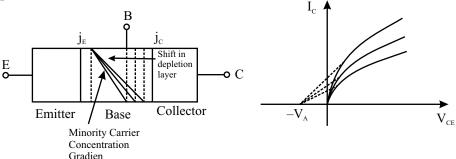

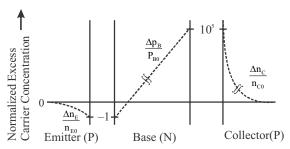

| 3.3  | Modes of                             | f Operation of BJT and Minority Carrier Distribution            | 189        |  |  |

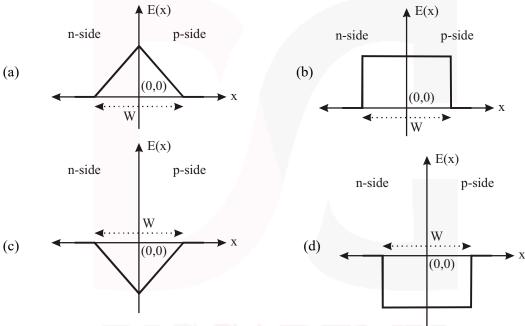

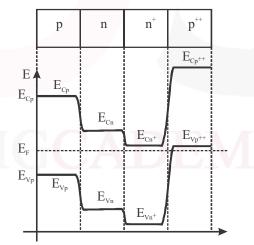

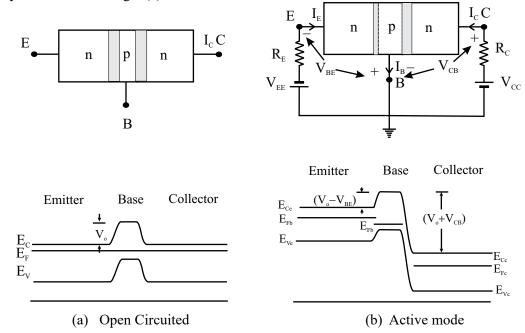

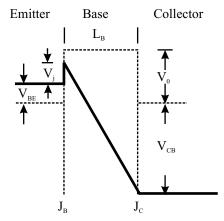

| 3.4  | Energy E                             | Band Diagram of BJT under Zero Bias and Active Mode             | 192        |  |  |

| 3.5  | Simplifie                            | ed Current Expressions of BJT                                   | 192        |  |  |

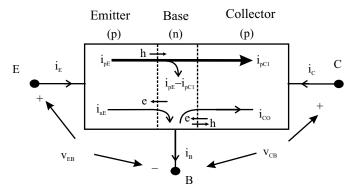

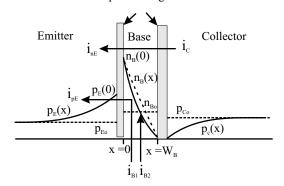

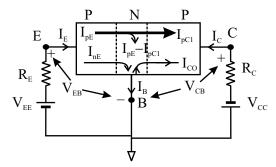

| 3.6  | Compon                               | ents of Current in BJT                                          | 199        |  |  |

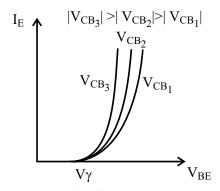

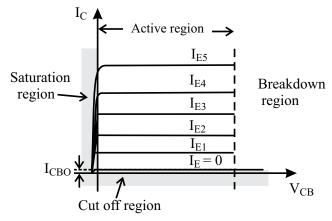

| 3.7  | Configur<br>3.7.1                    | rations of BJT<br>Common Base (CB) Configuration                | 204<br>204 |  |  |

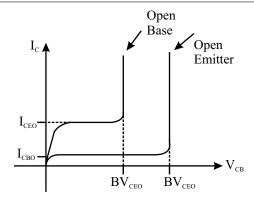

|      | 3.7.2                                | Common Emitter (CE) Configuration                               | 207        |  |  |

|      | 3.7.3                                | Common Collector Configuration                                  | 214        |  |  |

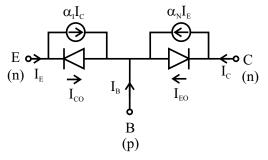

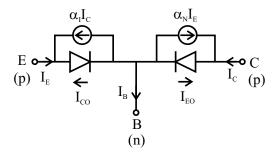

| 3.8  | Ebers-M                              | oll model of BJT                                                | 215        |  |  |

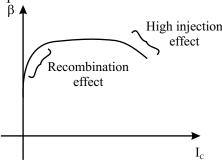

| 3.9  | Non-Idea                             | Non-Ideal Effects in BJT 216                                    |            |  |  |

| 3.10 | Switching Characteristics of BJT 220 |                                                                 |            |  |  |

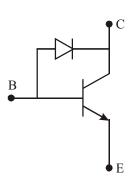

| 3.11 | Schottky Clamped Transistor                                  |                                                                                                                                                    |        |  |  |

|------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|

| 3.12 | Phototransistor                                              |                                                                                                                                                    |        |  |  |

| GATE | QUESTIC                                                      | ONS                                                                                                                                                | 224    |  |  |

| Answ | ers & Exp                                                    | lanations of GATE Questions                                                                                                                        | 230    |  |  |

| CHAP | TER 4 FE                                                     | Ts and MOS CAPACITOR 23                                                                                                                            | 37-346 |  |  |

| 4.1  | Introduc                                                     | tion                                                                                                                                               | 237    |  |  |

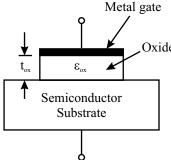

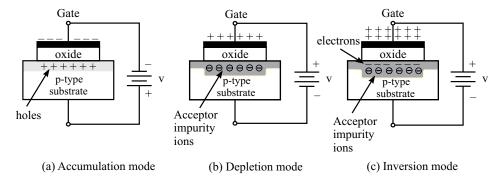

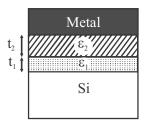

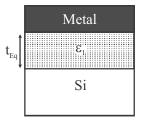

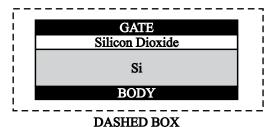

| 4.2  | Metal-Oxide-Semiconductor (MOS) Capacitor (Only for ECE)     |                                                                                                                                                    |        |  |  |

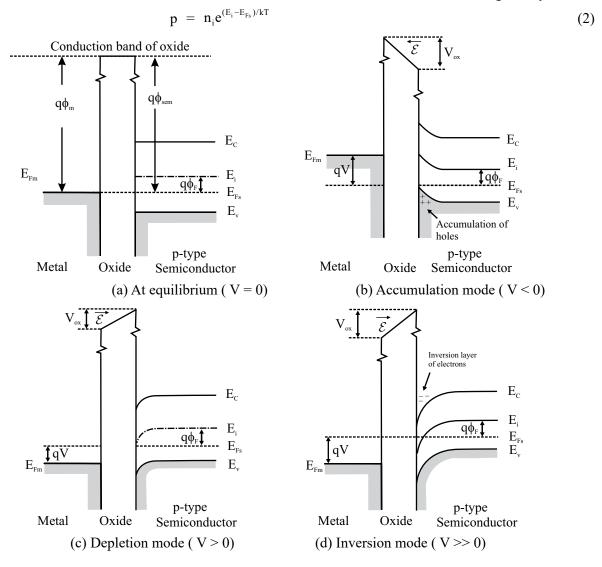

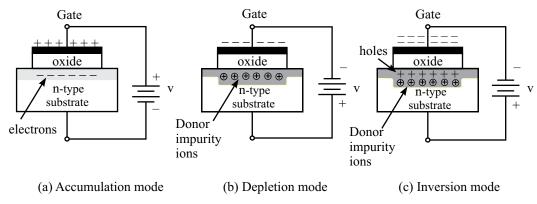

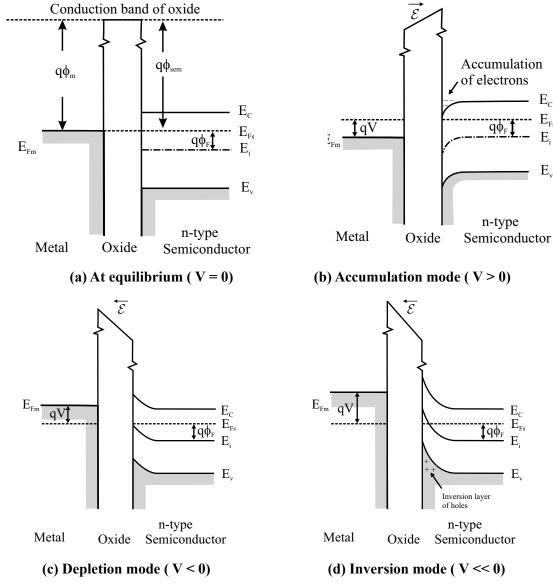

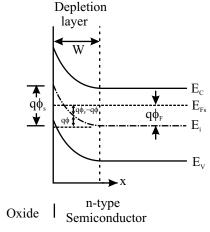

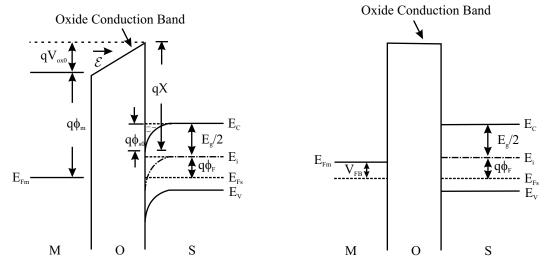

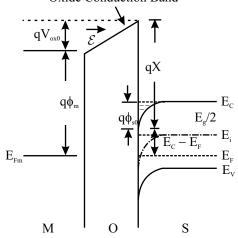

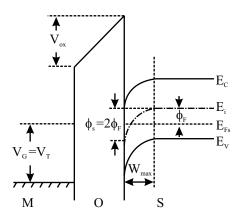

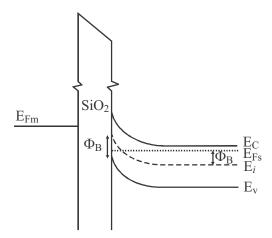

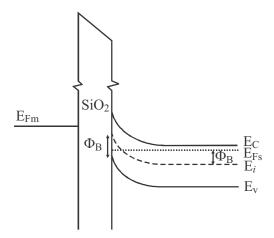

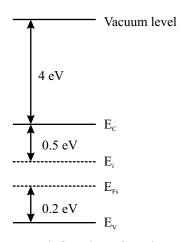

|      | 4.2.1                                                        | Energy Band Diagram of MOS Capacitor                                                                                                               | 239    |  |  |

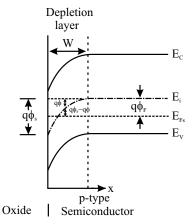

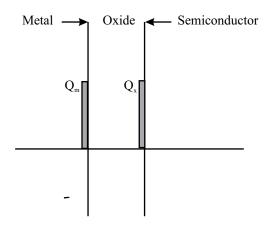

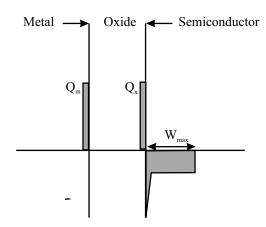

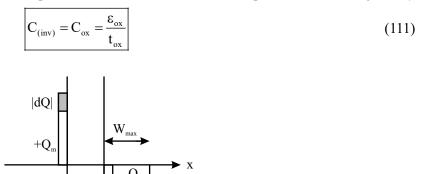

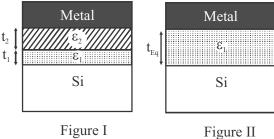

|      | 4.2.2                                                        | Surface Potential, Carrier Concentration and Depletion Region<br>Width in MOS Capacitor in Inversion Mode                                          | 244    |  |  |

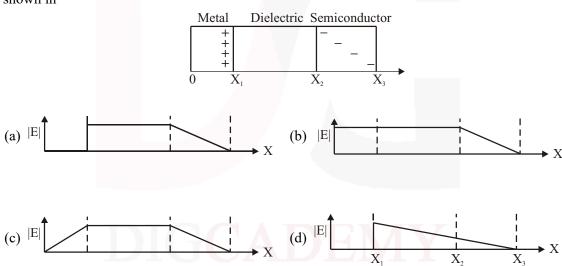

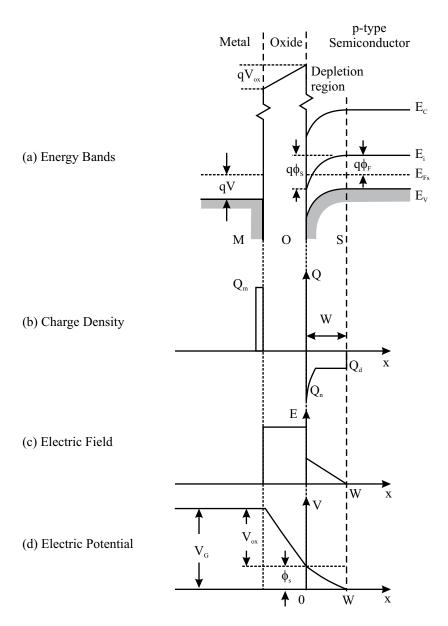

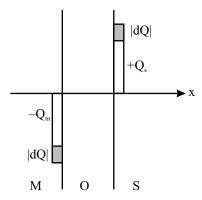

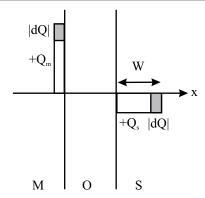

|      | 4.2.3                                                        | Charge Distribution, Electric Field and Electric Potential in MOS capacitor                                                                        | 250    |  |  |

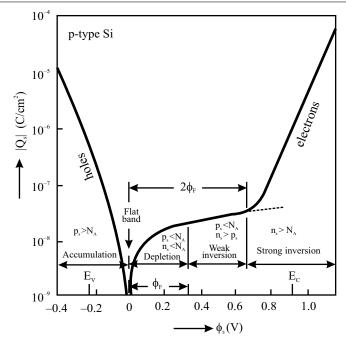

|      | 4.2.4                                                        | Variation of surface charge density as a function of surface                                                                                       | 254    |  |  |

|      |                                                              | potential                                                                                                                                          |        |  |  |

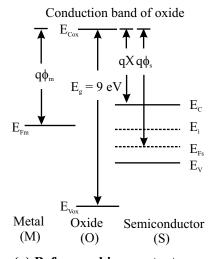

|      | 4.2.5                                                        | Work Function Difference                                                                                                                           | 255    |  |  |

|      | 4.2.6                                                        | Flat Band Voltage                                                                                                                                  | 257    |  |  |

|      | 4.2.7                                                        | Threshold Voltage                                                                                                                                  | 261    |  |  |

|      | 4.2.8                                                        | Gate Voltage at Strong Inversion                                                                                                                   | 262    |  |  |

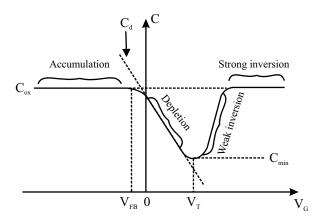

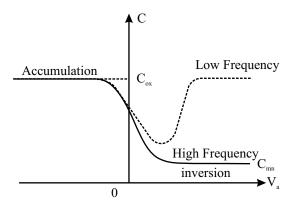

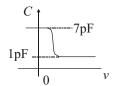

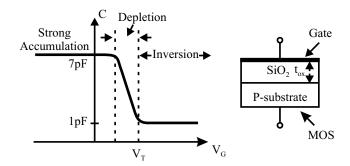

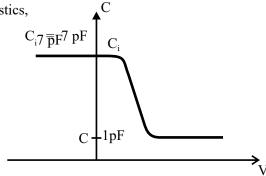

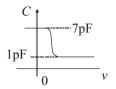

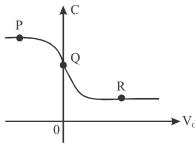

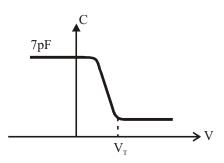

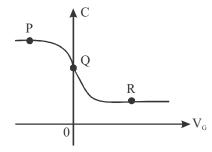

|      | 4.2.9                                                        | Capacitance-Voltage Characteristics of MOS Capacitor                                                                                               | 265    |  |  |

| 4.3  | Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs) |                                                                                                                                                    |        |  |  |

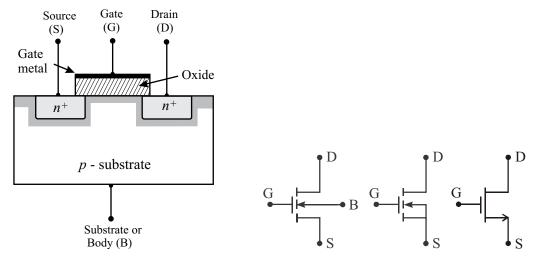

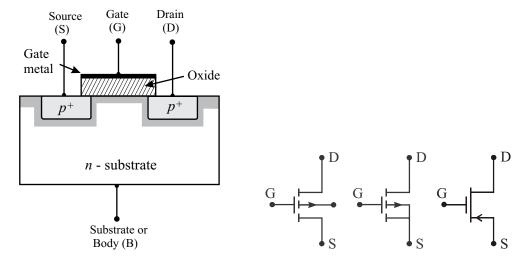

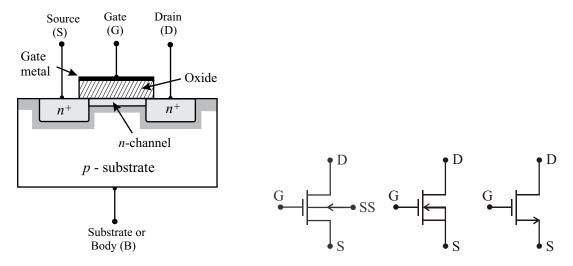

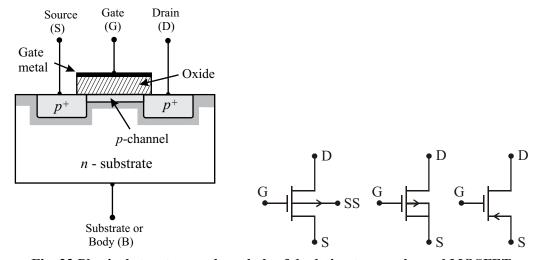

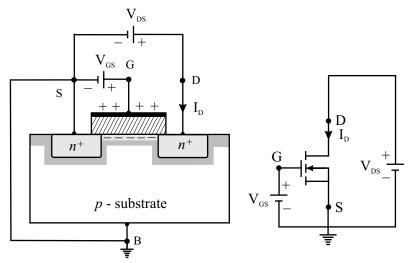

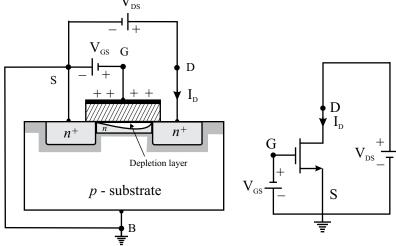

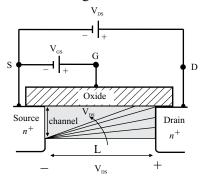

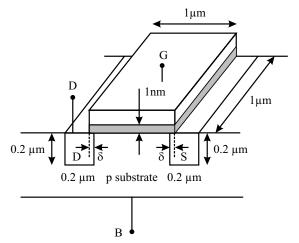

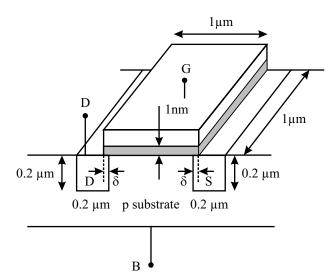

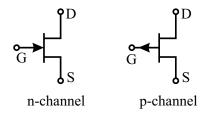

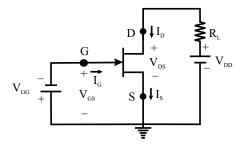

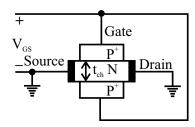

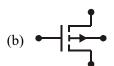

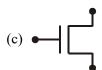

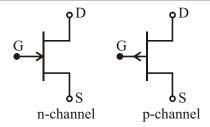

|      | 4.3.1                                                        | Physical Structure and Symbols of MOSFET                                                                                                           | 272    |  |  |

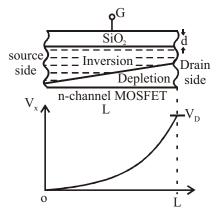

|      | 4.3.2                                                        | Operation of MOSFET                                                                                                                                | 274    |  |  |

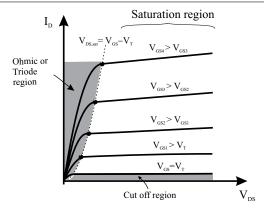

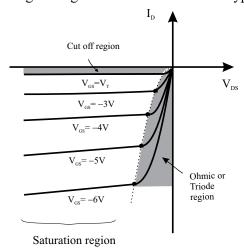

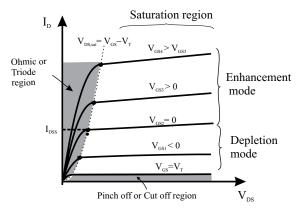

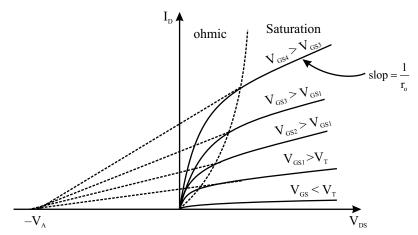

|      | 4.3.3                                                        | Output or Drain characteristics of MOSFET                                                                                                          | 276    |  |  |

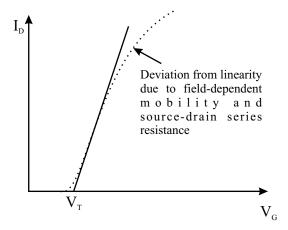

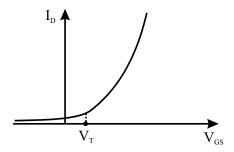

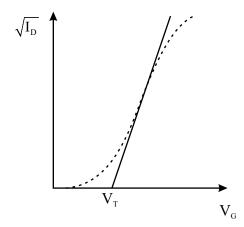

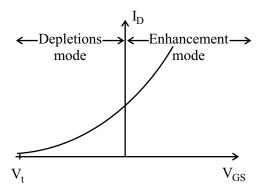

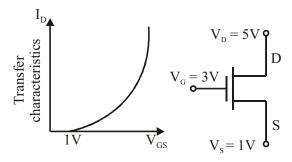

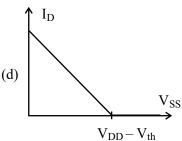

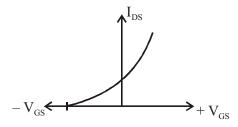

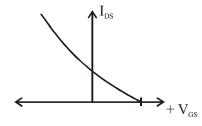

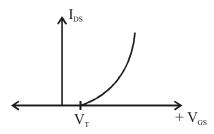

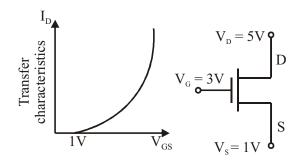

|      | 4.3.4                                                        | Transfer characteristic of MOSFETs                                                                                                                 | 281    |  |  |

|      | 4.3.5                                                        | Control of Threshold Voltage of MOSFET                                                                                                             | 284    |  |  |

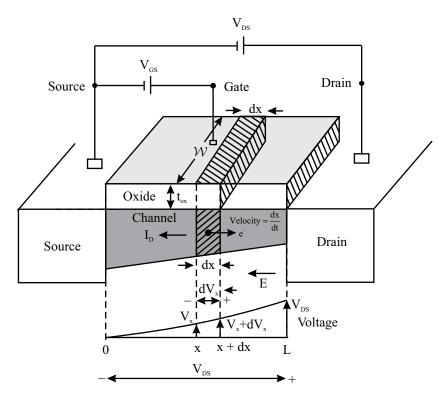

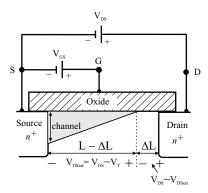

|      | 4.3.6                                                        | Derivation of $\boldsymbol{I}_{\!\scriptscriptstyle D}\text{-}\boldsymbol{V}_{\!\scriptscriptstyle DS}$ Relationship of Enhancement type n-channel | 286    |  |  |

|      |                                                              | MOSFET                                                                                                                                             |        |  |  |

|      | 4.3.7                                                        | Channel Resistance in ohmic region or ON resistance of n-channel                                                                                   | el     |  |  |

|      |                                                              | MOSFET                                                                                                                                             | 295    |  |  |

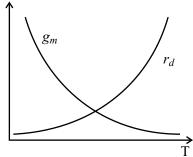

|      | 4.3.8                                                        | Non-ideal Effects in MOSFETs                                                                                                                       | 298    |  |  |

|      | 439                                                          | MOSEET Scaling                                                                                                                                     | 304    |  |  |

|      | 4.3.10    | Breakdown and Gate protection of MOSFET                      | 305 |

|------|-----------|--------------------------------------------------------------|-----|

|      | 4.3.11    | Comparison of Enhancement and Depletion type MOSFETs         | 305 |

|      | 4.3.12    | Comparison between p-channel and n-channel MOSFET            | 305 |

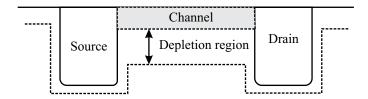

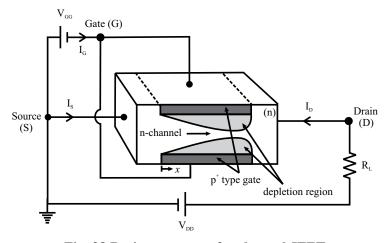

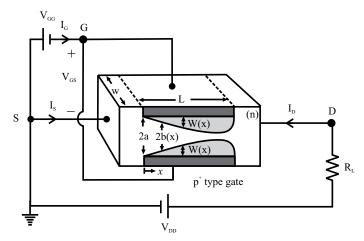

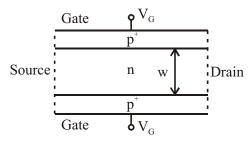

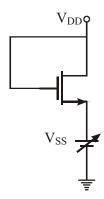

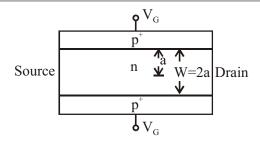

| 4.4  | Junction  | a Field Effect Transistor (JFET) ( No more in GATE syllabus) | 307 |

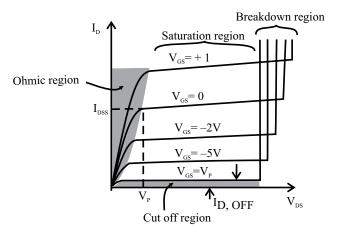

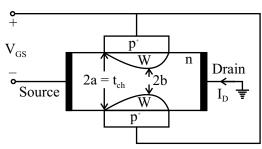

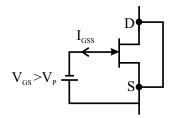

|      | 4.4.1     | Operation of JFET                                            | 308 |

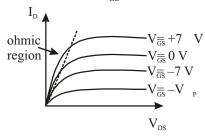

|      | 4.4.2     | Static Drain Characteristics of JFET                         | 308 |

|      | 4.4.3     | Expression for pinch off voltage                             | 311 |

|      | 4.4.4     | Volt-ampare characteristic of JFET for ohmic region          | 312 |

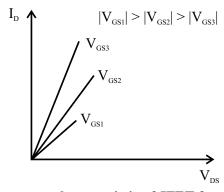

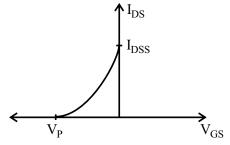

|      | 4.4.5     | Transfer characteristics of JFET                             | 316 |

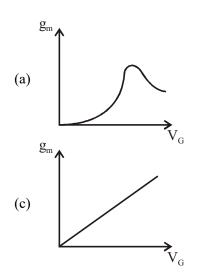

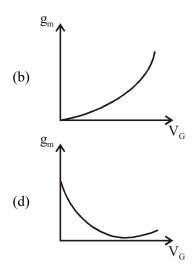

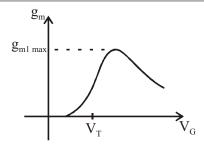

|      | 4.4.6     | Transconductance of JFET                                     | 317 |

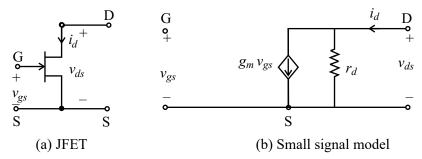

|      | 4.4.7     | Small Signal Model of FET                                    | 318 |

|      | 4.4.8     | Comparison between JFET and MOSFET parameters                | 320 |

| GATE | E QUESTIC | ONS                                                          | 321 |

| Answ | ers and E | xplanations of GATE Ouestions                                | 331 |

### \* HOW TO READ THIS BOOK \*

This book has been designed to meet the requirement of all Electrical, Electronics and Instrumentation Engineers. It is has been written in simple and lucid language so that students from all backgrounds, having little knowledge of English, can understand. It is designed to develop facts and concepts for competitive examinations in India like GATE, IES, PSUs and IAS examinations. The book can be referred for University Syllabus across different countries in the world. Every chapter is followed and prepared after in depth analysis of previous year questions which appeared in these competitive examinations. The focus is mainly on developing concepts along with facts. Each chapter has been followed by previous years fully solved questions of GATE of Electronics, Electrical and Instrumentation Engineering. These questions are helpful for university examination also.

#### For students studying in B.E./B.Tech

This book would help students studying in B.Tech to prepare for their university examination. In parallel book is equipped to prepare B.Tech students for competitive examinations like GATE and ESE. However, main focus of students of B.Tech should be to develop concepts and then practice question of GATE.

#### For students preparing for GATE

The theory of this book has been prepared to develop theoretical concepts for those students who are preparing for GATE. Such students should focus on theoretical concepts followed by practicing previous year GATE questions which are given at the end of each chapter along with full solutions. Students first try to solve the question themselves and the refer the solution.

#### For students preparing for ESE Preliminary

The theory of this book has been prepared for students preparing for ESE both Electrical and Electronics Preliminary and Mains Examinations and IAS Electrical mains examination. However, students preparing for ESE Pre examination should note down factual information and formulas in their notebook in form of brief notes. It helps in quick revision just before the Pre examination. Each chapter has been provided with fully solved questions of ESE Pre for both EE and EC. Students should practice these questions in time bound manner with one question in one minute. It would help to build speed and accuracy. Solutions should be referred only to clarify doubt if any.

#### For students preparing for ESE Mains and IAS Mains

The students preparing for ESE Mains of EE and EC or IAS Electrical mains should practice questions from all these examination so that they have enough practice questions. However, solutions of these question will be provided in next edition of this book. Such students should not wast much time on reading theory in whole they should relevant portion which are important for mains examination as they have already studied the whole theory while preparing for preliminary stage.

#### PREFACE TO FIRST EDITION

#### Chapter 1

Chapter 1 gives an introduction to semi-conducting materials, their types and energy band diagrams. It also describes the electrical properties of semiconductors, their Fermi levels and mechanism of flow of current. This chapter is important for GATE EC, ESE Pre for EE and EC and ESE mains for EC.

#### Chapter 2

Chapter 2 introduces the PN junctions and their behaviour under forward and reverse biased conditions, components of diode current. It also introduces the diode capacitances and resistances. Different types of diodes and their operational features are also discussed in detail. This topic is important for all the competitive examination of Electrical, Electronics and Instrumentation engineers.

#### Chapter 3

Chapter 3 Introduces bipolar junction transistors, their characteristics, configurations and current components. It is important topic for understanding of operations of BJT based amplifiers. This chapter is important for GATE examination of EE, EC and ESE pre examinations of EE and EC.

#### Chapter 4

Chapter 4 Explains MOS Capacitor, Construction and operation of MOSFETs and JFETs. It is important mainly for GATE EC and ESE Pre and mains of EC and EE. This chapter is important for understanding of amplifier circuits based MOSFET and JFETs.

#### CHAPTERWISE GATE SYLLABUS

| Chap. | Торіс                                     | Electronics & Comm.<br>Engineering                                                                                                                                                                                                                                                                | Electrical<br>Engineering                                   | Instrumentation<br>Engineering                         |

|-------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------|

| Ch.1  | Semiconductors                            | Energy bands in intrinsic and extrinsic semiconductors, equilibrium carrier concentration, direct and indirect band-gap semiconductors, Carrier transport: diffusion current, drift current, mobility and resistivity, generation and recombination of carriers, Poisson and continuity equations |                                                             |                                                        |

| Ch.2  | Diodes                                    | P-N junction, Zener diode,<br>LED, photo diode and solar<br>cell                                                                                                                                                                                                                                  |                                                             | Characteristics and applications of diode, Zener diode |

| Ch.3  | Bipolar Junction<br>Transistors           | ВЈТ                                                                                                                                                                                                                                                                                               |                                                             | Characteristics and applications of BJT                |

| Ch.4  | Field Effect<br>Transistors               | MOSFET & MOS Capacitor                                                                                                                                                                                                                                                                            |                                                             | Characteristics<br>and applications of<br>MOSFET       |

| Ch.5  | Diodes Circuits                           | Diode circuits: clipping, clamping and rectifiers.                                                                                                                                                                                                                                                | Simple diode<br>circuits: clipping,<br>clamping, rectifiers |                                                        |

| Ch.6  | BJT Biasing<br>& Thermal<br>Stabilization | BJT amplifiers: biasing                                                                                                                                                                                                                                                                           | Amplifiers: Biasing                                         |                                                        |

| Ch.7  | MOSFET<br>Biasing                         | MOSFET amplifiers: biasing                                                                                                                                                                                                                                                                        | Amplifiers: Biasing                                         |                                                        |

| Ch.8  | Small Signal<br>Analysis of BJT           | BJT amplifiers: ac coupling, small signal analysis                                                                                                                                                                                                                                                | Amplifiers:<br>Equivalent circuit                           | small signal analysis of<br>transistor circuits        |

| Ch.9  | Small Signal<br>Analysis of FET           | MOSFET amplifiers: ac coupling, small signal analysis                                                                                                                                                                                                                                             | Amplifiers:<br>Equivalent circuit                           | small signal analysis of<br>transistor circuits        |

| Chap. | Торіс                                 | Electronics & Comm.                                                                                                   | Electrical                                                                                                                      | Instrumentation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                       | Engineering                                                                                                           | Engineering                                                                                                                     | Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Ch10  | Frequency                             | BJT and MOSFET amplifiers                                                                                             | Amplifiers:                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | Response                              | : frequency response                                                                                                  | Frequency response                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Ch.11 | Multistage<br>Amplifiers              |                                                                                                                       |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Ch.12 | Compound                              | BJT and MOSFET amplifiers                                                                                             |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|       | circuits                              | : Current mirror                                                                                                      |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Ch.13 | Feedback<br>Amplifiers                |                                                                                                                       | Feedback amplifiers                                                                                                             | Feedback amplifiers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Ch.14 | Differential<br>Amplifiers            | BJT and MOSFET amplifiers : differential amplifiers.                                                                  | BJT and MOSFET Differential Amplifiers                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Ch.15 | Operational Amplifiers & its circuits | Op-amp circuits: Amplifiers, summers, differentiators, integrators, active filters, Schmitt triggers and oscillators. | operational amplifiers: characteristics and applications; single stage active filters, Sallen Key, Butterworth, VCOs and timers | Characteristics of ideal and practical operational amplifiers; applications of opamps: adder, subtracter, integrator, differentiator, difference amplifier, instrumentation amplifier, precision rectifier, active filters, oscillators, signal generators, voltage controlled oscillators and phase locked loop, sources and effects of noise and interference in electronic circuited oscillators, signal generators, voltage locked oscillators, signal generators, voltage controlled oscillators, signal generators, voltage controlled oscillators and phase locked loop. |

| Ch.16 | Oscillators                           |                                                                                                                       | Oscillators                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Ch.17 | Power Supplies                        |                                                                                                                       |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Ch.18 | Power<br>Amplifiers                   |                                                                                                                       |                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### CHAPTERWISE ANALYSIS OF GATE QUESTIONS

| Ele   | Electronics and Communication Engineering : EDC & Analog Electronics |      |      |      |      |    |    |    |    |     |            |    |    |      |    |    |          |      |      |      |      |

|-------|----------------------------------------------------------------------|------|------|------|------|----|----|----|----|-----|------------|----|----|------|----|----|----------|------|------|------|------|

| Chap  | Topic                                                                | 2010 | 2011 | 2012 | 2013 |    |    | 14 |    |     | 2015       |    |    | 2016 |    |    | 17       | 2018 | 2019 | 2020 | 2021 |

| _     | •                                                                    | 4    | 1    |      |      | 7  | 2  | 3  | 1  | III | 6          | 1  | Ш  | 2    | 5  | Ш  | 5        |      |      | 1    | 2    |

| Ch.1  | Semiconductors                                                       |      | 1    |      |      | /  | _  | 3  |    |     | 0          | 1  |    | 2    | _  |    | <u> </u> |      |      | 1    |      |

| Ch.2  | Diodes                                                               | 2    | 2    |      | 1    |    | 3  |    | 4  |     |            | 5  | 4  | 4    | 2  | 4  | 3        | 12   | 10   | 5    | 2    |

| Ch.3  | BJT and Its Characteristics                                          | 2    | 2    |      |      | 2  |    | 1  | 2  | 3   |            |    | 2  | 1    |    | 1  | 1        |      | 1    | 2    |      |

| Ch.4  | FET and Its Characteristics                                          | 2    | 6    | 8    | 5    |    | 7  | 5  | 4  | 5   | 2          | 4  | 3  | 5    | 4  | 8  | 2        | 3    | 3    | 2    | 2    |

| Ch.5  | Diode circuits                                                       |      | 4    | 3    | 4    | 1  |    | 2  | 1  | 3   | 3          | 1  | 3  | 2    |    | 1  |          |      | 5    | 1    | 2    |

| Ch.6  | Biasing of BJT                                                       |      | 2    |      | 2    |    | 3  | 1  |    | 1   | )<br> <br> |    | 1  |      |    | 1  | 2        |      |      |      |      |

| Ch.7  | Biasing of MOSFET                                                    |      |      |      |      |    |    |    |    |     |            |    |    |      |    |    |          |      |      | 2    | 2    |

| Ch.8  | Small Signal Analysis of BJT                                         | 2    |      | 1    |      | 7  |    |    | 2  |     | 2          |    | 4  |      |    | 2  | 2        |      |      | 2    |      |

| Ch.9  | Small Signal Analysis of FET                                         | 2    |      | 1    |      | 7  |    |    | 2  |     | 2          |    | 4  |      |    | 2  | 2        |      |      | 2    | 1    |

| Ch.10 | Frequency Response                                                   | 4    | T    | 7    |      |    |    |    |    |     |            |    |    |      |    |    | 1        |      |      |      |      |

| Ch.11 | Multistage Amplifiers                                                |      |      |      |      |    |    | 1  |    |     |            |    |    | 1    |    |    |          |      |      |      |      |

| Ch.12 | Compoud circuits                                                     | 1    |      |      |      |    |    |    |    |     |            |    |    | 1    |    |    |          |      | 4    |      |      |

| Ch.13 | Feedback Amplifiers                                                  |      |      | 2    | 1    |    | 1  | 1  | 1  |     |            |    |    |      |    |    | 1        | 1    |      |      |      |

| Ch.14 | Differential Amplifiers                                              |      |      |      |      |    |    | 1  |    |     |            | 2  |    |      |    |    |          |      |      |      |      |

| Ch.15 | Operational Amplifiers & its circuits                                | 3    | 1    | 2    | 3    | 2  | 2  |    | 6  | 3   | 6          | 4  | 3  | 4    | 8  | 2  | 3        | 4    |      | 4    | 4    |

| Ch.16 | Oscillators                                                          |      |      |      |      |    |    |    |    |     |            |    |    |      |    |    |          |      |      |      |      |

| Ch.17 | Power Supplies                                                       |      |      |      |      |    |    |    |    |     |            |    |    |      |    |    |          |      |      | 2    |      |

| Ch.18 | Power Amplifiers                                                     |      |      |      |      |    |    |    |    |     |            |    |    |      |    |    |          |      |      |      |      |

|       | Total Marks                                                          | 22   | 18   | 14   | 16   | 26 | 18 | 19 | 22 | 15  | 21         | 17 | 24 | 20   | 19 | 21 | 22       | 20   | 23   | 23   | 15   |

|       | Electrical Engineering : EDC & Analog Eectronics |      |      |      |      |    |     |     |   |     |      |   |     |      |   |   |    |      |      |      |      |

|-------|--------------------------------------------------|------|------|------|------|----|-----|-----|---|-----|------|---|-----|------|---|---|----|------|------|------|------|

| Chap  | Topic                                            | 2010 | 2011 | 2012 | 2013 |    |     | )14 |   |     | 2015 |   |     | 2016 | _ | _ | 17 | 2018 | 2019 | 2020 | 2021 |

| Ch.1  | Semiconductors                                   |      |      |      |      | IV | III | П   | - | III | П    |   | III | II   | - | П | 1  |      |      |      |      |

| Ch.2  | Diodes                                           |      |      |      |      |    |     |     |   |     |      |   |     |      |   |   |    |      |      | 2    |      |

| Ch.3  | BJT and Its Characteristics                      |      |      |      |      |    |     |     |   |     | 1    |   |     |      |   |   |    |      |      | 1    |      |

| Ch.4  | FET and Its Characteristics                      |      |      |      |      |    |     |     |   |     |      |   |     |      |   |   |    |      | 1    | 2    |      |

| Ch.5  | Diode circuits                                   |      | 2    | 2    | 4    |    |     | 2   |   |     | 2    |   |     |      | 3 |   |    |      |      |      | 4    |

| Ch.6  | BJT Biasing                                      |      | 2    | 2    |      |    |     |     |   |     | 1    | 1 |     |      | 1 | 2 |    | 2    | 2    | 2    | 1    |

| Ch.7  | FET Biasing                                      |      |      |      |      |    |     |     |   |     |      | 7 |     |      |   |   |    |      |      |      |      |

| Ch.8  | Small Signal Analysis of BJT                     |      |      |      |      |    |     | 1   | 2 | 1   |      |   |     |      |   |   |    |      |      | 1    |      |

| Ch.9  | Small Signal Analysis of FET                     |      |      |      |      |    |     |     |   |     |      |   |     |      |   |   |    |      |      |      |      |

| Ch.10 | Frequency Response of BJT & MOSFET               |      | T    | 7    |      |    |     |     |   |     |      |   |     |      |   |   |    |      |      |      |      |

| Ch.11 | Multistage Amplifiers                            |      |      |      |      |    |     |     |   |     |      |   |     |      |   |   |    |      |      |      |      |

| Ch.12 | Compoud circuits                                 |      |      |      |      |    |     |     |   |     |      |   |     |      |   |   |    |      |      |      |      |

| Ch.13 | Feedback Amplifiers                              |      |      | 2    | 1    |    |     |     |   |     |      |   |     |      |   |   |    |      | 1    |      |      |

| Ch.14 | Differential Amplifiers                          |      |      |      |      |    |     |     |   |     |      |   |     |      |   |   | 2  |      |      | 2    |      |

| Ch.15 | Operational Amplifiers & its circuits            | 1    | 1    | 4    | 3    |    | 3   | 2   | 3 |     | 4    | 4 |     | 3    |   | 2 | 2  |      | 2    |      | 2    |

| Ch.16 | Oscillators                                      |      |      |      |      |    |     |     |   |     |      |   |     |      |   |   |    |      |      |      |      |

| Ch.17 | Power Supplies                                   |      |      |      |      |    |     |     |   |     |      |   |     |      |   |   |    |      |      | 2    |      |

| Ch.18 | Power Amplifiers                                 |      |      |      |      |    |     |     |   |     |      |   |     |      |   |   |    |      |      |      |      |

|       | Total Marks                                      | 1    | 5    | 10   | 8    |    | 3   | 4   | 5 | 1   | 8    | 5 |     | 3    | 4 | 4 | 4  | 2    | 6    | 12   | 7    |

|       | Instrumentation Engineering : EDC & Analog Eectronics |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

|-------|-------------------------------------------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| Chap  | Topic                                                 | 2010 | 2011 | 2012 | 2013 | 2014 | 2015 | 2016 | 2017 | 2018 | 2019 | 2020 | 2021 | 2022 | 2023 | 2024 |

| Ch.1  | Semiconductors                                        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.2  | Diodes and theirs circuits                            |      |      |      |      |      |      | 3    | 2    |      | 1    |      |      |      |      |      |

| Ch.3  | BJT & Its Characteristics                             |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.4  | FET Characteristics and its biasin                    |      |      |      |      |      | 2    |      | 2    |      |      |      |      |      |      |      |

| Ch.5  | Diodes Circuits                                       |      | 2    | 2    | 4    | 1    | 1    |      | 1    | 1    | 1    | 3    |      |      |      |      |

| Ch.6  | BJT Biasing                                           |      |      |      | 1    | 4    | 2    |      |      |      |      |      |      |      |      |      |

| Ch.7  | FET Biasing                                           |      |      |      |      |      |      |      |      | 1    |      |      |      |      |      |      |

| Ch.8  | Small Signal Analysis of BJT                          |      | 1    |      | 1    |      | 2    |      |      |      | 2    |      |      |      |      |      |

| Ch.9  | Small Signal Analysis of FET                          |      |      |      |      |      |      |      | 12   |      |      |      |      |      |      |      |

| Ch.10 | Frequency Response of BJT & MOSFET                    |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.11 | Multistage Amplifiers                                 |      |      | 1    |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.12 | Compound circuits                                     | 2    | NE   |      |      |      |      |      |      |      | 2    |      | 3    |      |      |      |

| Ch.13 | Feedback Amplifiers                                   | V    | 3    |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.14 | Differential Amplifiers                               |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.15 | Operational Amplifiers                                | 7    | 11   | 2    | 12   | 8    | 4    | 15   | 8    | 7    | 3    |      | 5    |      |      |      |

| Ch.16 | Oscillators                                           |      |      |      |      |      |      |      | 1    |      |      | 9    |      |      |      |      |

| Ch.17 | Power Supplies                                        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.18 | Power Amplifiers                                      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.19 | Tuned Amplifiers                                      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| Ch.20 | Multivibrators                                        |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

|       | Total Marks                                           | 9    | 14   | 4    | 18   | 13   | 11   | 18   | 14   | 8    | 9    | 12   | 8    |      |      |      |

Ch

#### **Semiconductors**

#### 1.1 Atomic Structure of Materials

The understanding of atomic structure is an important step to under stand the structure of solids including semiconductors. Rutherford found that atoms consists of a nucleus of positive charge consisting protons. The nucleus is surrounded by negatively charged particles called electrons. The number of protons in nucleus is same as the number of electrons. The electrons revolve around the nucleus in closed orbit.

According to Bohr postulates the electrons around the nucleus always occupies discrete energy level. The energy of electron in Joules at n<sup>th</sup> level is given by,

$$W_{n} = -\frac{mq^{4}}{8h^{2}\varepsilon_{0}^{2}} \frac{1}{n^{2}} \tag{1}$$

where h is plank's constant, m is mass & q is charge of electron and  $\varepsilon_0$  is dielectric constant of free space.

When atom is exposed to a photon, the electron can shift from one energy level to another level if the energy of photon is equal to energy difference between two energy levels. The electron can again fall back to its normal state by emitting photons having energy equal to the deference in energy levels.

The electrons around the nucleus are located in shells. There are four quantum number associated with an electron in a shell. These quantum numbers are known as n,l,m ans s.

The these quantum numbers are restricted to following integral values,

n = 1, 2, 3

$$l = 0,1,2,3., (n-1)$$

m = 0, ±1, ±2, ±3 . ± $l$

$s = \pm 1/2$

According to Pauli's exclusion principle no two electrons can have same set of quantum numbers in an atom. All electrons having same value of n belong to same electronic shell identified by K,L,M & N corresponding to n = 1,2,3,4... The shell are divided in sub-shell corresponding to different value of l and identified by s,p,d,

The atomic number and electronic configurations of important semiconductors are given in below,

| Element | Atomic No. | Configuration                                        |

|---------|------------|------------------------------------------------------|

| C       | 6          | $1s^22s^22p^2$                                       |

| Si      | 14         | $1s^22s^22p^63s^23p^2$                               |

| Ge      | 32         | $1s^22s^22p^63s^23p^63d^{10}4s^24p^2$                |

| Sn      | 50         | $1s^22s^22p^63s^23p^63d^{10}4s^24p^64d^{10}5s^25p^2$ |

It is observed that the outer most shell in all the atoms of goup IV has four electrons.

Note: The energy state of the electrons in an atom can be determined by using Schrödinger equation (Schrödinger-equation).

#### 1.2 Bonding in solids

Atoms are rarely found as free and independent units, but usually are linked or bonded to other atoms in some manner as a result of inter-atomic forces. The forces between two atoms or ions is function of distance. This force is repulsive when separation is small and attractive when separation is large. A particular separation the force of repulsion is equal to force of attraction and net force is zero. These bonding forces between the atoms are called chemical bonds and the process of holding them is called bonding. According to strength chemical bonds are grouped in to two groups called primary bonds and secondary bonds. The primary bonds are three types called Ionic, Covalent and Metallic Bonds. **Ionic bond** is a simplest type of primary bond. Ionic bonding forms between two oppositelycharged ions which are produced by the transfer of electrons from one atom to another. The positive and negative ions have a natural attraction from each other, producing a strong bonding force. The ionic bond is said to be non-directional. Covalent bonds are formed by the sharing of electrons between neighboring atoms. In this type of bond, the atoms being linked find it impossible to produce complete shells by electron transfer, but achieve the same goal by electron sharing so that each attain a stable electronic structure. Moreover, the shared negative electrons locate between the positive and negative nuclei to form the bonding link. This also gives directionality to the covalent bond. Some of the materials having covalent bond are Carbon, Silicon, Germanium, Gray tin etc. Metallic Bonds are exhibited by the elements to the left of the fourth column in the periodic table, having small number of valence electrons. The Van der Waals Bonds are weak or secondary bonds which can link molecules that posses a non-symmetric distribution of atoms.

**Note:** The Semiconductor atoms of Group-IV exhibits the covents bonds.

#### 1.3 Crystal Geometry and Structure

A crystal is a solid whose constituents molecules or atoms are arranged in a systematic pattern. In crystalline solids the pattern of atoms is repeated periodically. The solids which are non-crystalline the internal structure is not based on repeated patterns.

#### Space Lattice

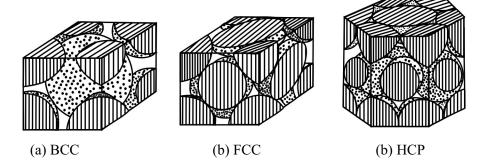

A space lattice is an infinite array of points in three dimensions in which every point has surroundings identical to those of every other point in the array. A unit cell is smallest unit of a space lattice. Space lattices of various materials differ in shape and size of their unit cells. Crystals of most of metals have highly symmetrical structures with closed packed atoms. The most common types of space lattices are Body centered cubic(BCC), Face centered cubic(FCC) and Hexagonal closed packed(HCP) as shown in

Fig. 1 Unit cells of BCC, FCC and HCP

The basic crystal structure of many important semiconductors is FCC lattice with a basis of two atoms giving rise to the Diamond structure, characteristic of Si, Ge and C in the diamond form. In many compound semiconductors formed with Group III-V compounds, the atoms are arranged in a basic diamond structure but sub-lattices of different atoms are inter-penetrated resulting in a structure called zinc blende structure.

**Note:** Si and Ge has FCC lattice and Diamond structure and GaAs has FCC sub-lattices of Ga and As inter-penetrating resulting in zinc blende structure.

#### 1.4 Energy Band Theory of Crystals

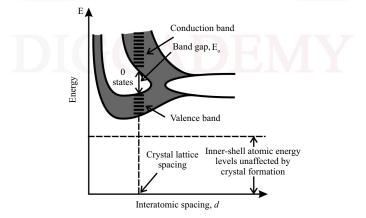

When atoms form crystals, it is found that the energy levels of the inner-shell electrons are not affected appreciably by the presence of the neighboring atoms. However, the levels of the outer-shell electrons are changed considerably, since these electrons are shared by more than one atom in the crystal. The new energy levels of the outer electrons can be determined by means of quantum mechanics and it is found that coupling between the outer-shell electrons of the atoms results in a band of closely spaced energy states, instead of the widely separated energy levels of the isolated atom.

Fig. 2 Splitting of energy levels of isolated atoms to energy bands

The energy band is split into two bands called valence band and conduction band. The valence band consists of empty energy states and conduction band consists of filled energy states. There is an energy gap between the valence and conduction bands called band gap decreases as the atomic

spacing decreases. The band gap ( $E_g$ ) is measured in electron-volt(eV). One electron-volt is equal to  $1.6 \times 10^{-19}$  Joules.

#### 1.5 Insulators, Semiconductors and metals

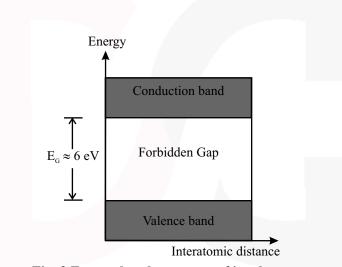

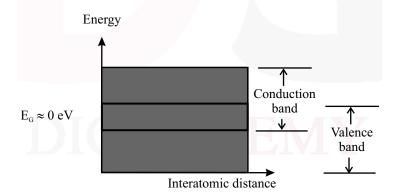

A very poor conductor of electricity is called an *insulator*; an excellent conductor is a *metal*; and a substance whose conductivity lies between these extremes is a *semiconductor*. A material may be placed in anyone of these three classes, depending upon its energy-band structure.

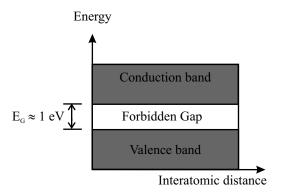

**Insulators**: The materials have large band gap of order of 6eV or more. This large forbidden band separates the filled valence region from the vacant conduction band as shown in Fig.3. In such materials the energy which can be supplied to an electron from an applied field is too small to carry the electron from the filled valence band to vacant conduction band. Since the electron cannot acquire sufficient applied energy, conduction is impossible, and hence they are an *insulator*. Therefore, the resistance of these materials is very high normally of order of mega-ohms.

Fig. 3 Energy band structure of insulators

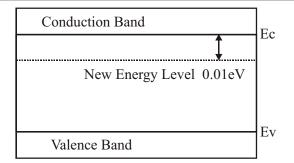

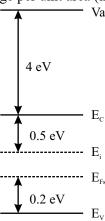

**Semiconductors**: A substance for which the width of the forbidden energy region is relatively small ( $\sim 1 \text{ eV}$ ) is called a *semiconductor*. Graphite, a crystalline form of carbon but having a crystal symmetry which is different from diamond, has such a small value of  $E_G$ , and it is a semiconductor.

Fig. 4 Energy band structure of semiconductors

The most important practical semiconductor materials are germanium and silicon, which have values of  $E_{\rm G}$  of 0.785 and 1.21 eV, respectively, at 0°K. Energies of this magnitude normally cannot be acquired from an applied field. Hence the valence band remains full, the conduction band empty, and these materials are insulators at low temperatures. However, the conductivity increases with temperature. These substances are known as *intrinsic semiconductors*.

As the temperature is increased, some of these valence electrons acquire *thermal* energy greater than  $E_G$ , and hence move into the conduction band. These are now free electrons in the sense that they can move about under the influence of even a small applied field. The insulator has now become slightly conducting; it is a *semiconductor*. The absence of an electron in the valence band is called a *hole*. Since, there is generation of electron and hole pair with increase in temperature, therefore, resistance of semiconductors decreases with increase in temperature. Because of this characteristic semiconductors are said to be having negative temperature coefficient.

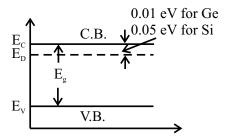

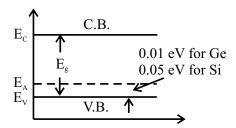

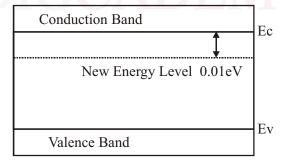

If certain impurity atoms are introduced into the crystal, these result in allowable energy states which lie in the forbidden energy gap. These impurity levels also contribute to the conduction. A semiconductor material where this conduction mechanism predominates is called an *extrinsic semiconductor*.

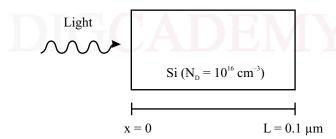

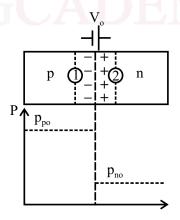

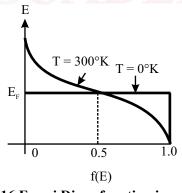

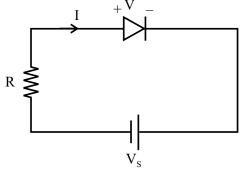

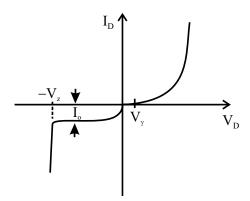

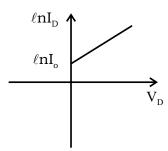

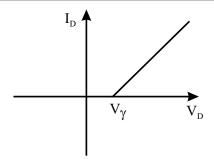

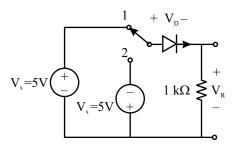

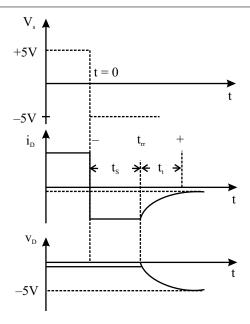

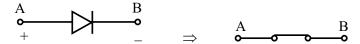

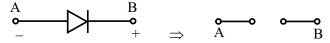

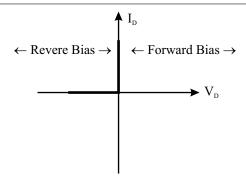

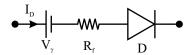

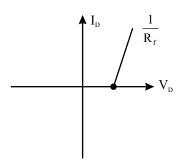

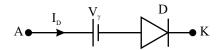

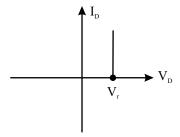

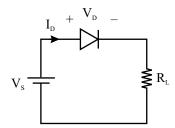

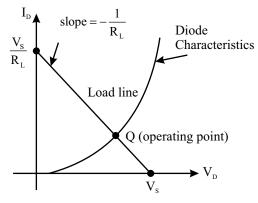

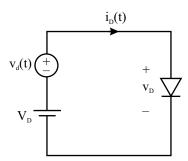

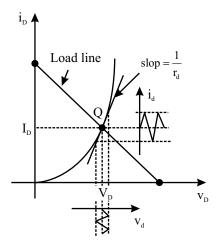

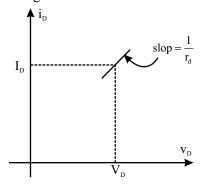

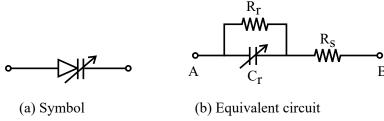

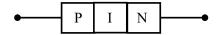

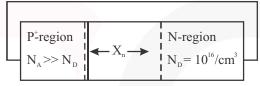

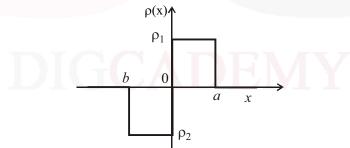

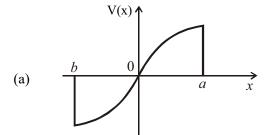

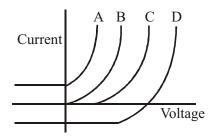

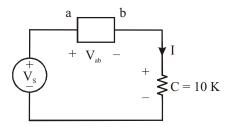

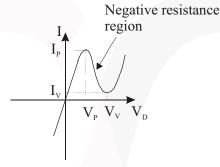

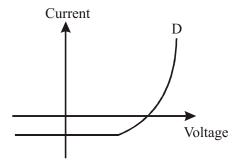

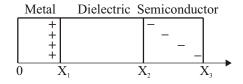

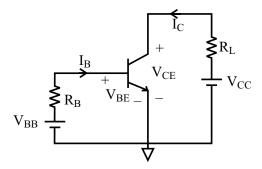

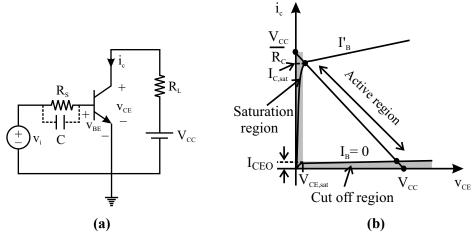

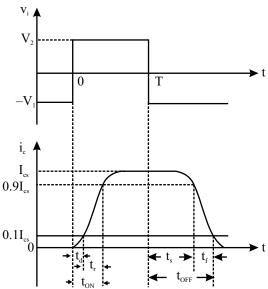

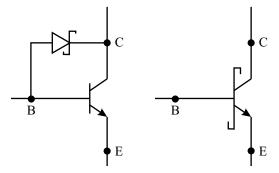

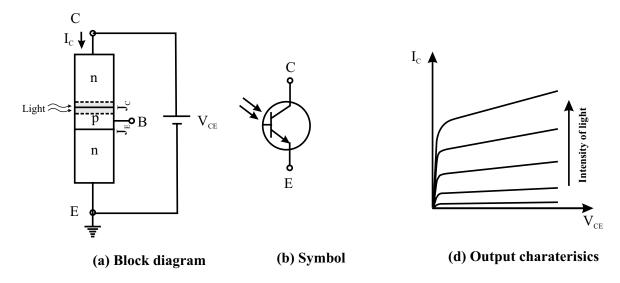

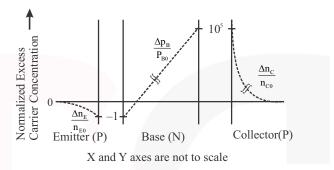

Since the band-gap energy of a crystal is a function of inter-atomic spacing as well as temperature. The band gap decreases with increase in temperature.